## Politecnico di Milano – Sede di Cremona Anno Accademico 2018/2019

# Architettura dei Calcolatori e Sistemi Operativi

Esame - 24.1.2019

**Prof. Carlo Brandolese**

| Cognome   | Nome  |

|-----------|-------|

|           |       |

| Matricola | Firma |

#### Istruzioni

- 1. Scrivere con cura, negli spazi sopra segnati, il proprio cognome, nome, numero di matricola e apporre la firma.

- 2. È vietato consultare libri, eserciziari, appunti ed utilizzare la calcolatrice e qualunque strumento elettronico (inclusi i cellulari), pena l'invalidazione del compito.

- 3. Il testo, debitamente compilato, deve essere riconsegnato in ogni caso.

- 4. Il tempo della prova è di 3 ore

#### **Valutazione**

| Domanda | Voto | Note |

|---------|------|------|

| А       |      |      |

| В       |      |      |

| С       |      |      |

| D       |      |      |

| E       |      |      |

| F       |      |      |

Si consideri la seguente funzione per il calcolo del massimo comun divisore:

```

int gcd( int a, int b)

{

while( a != b )

{

if( a > b )

a = a - b;

else

b = b - a;

}

return a;

}

```

Si traduca la funzione in assembly MIPS

| D | n | m | a | n | d | а | В |

|---|---|---|---|---|---|---|---|

| u | u |   | a |   | u | а | ப |

|   |     |     | essore MIPS dotato di una pipeline standard a cinque stadi, senza conoscimento dei conflitti. Sia inoltre dato il seguente codice assembly: |

|---|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | ADD | R5. | R2, R1                                                                                                                                      |

| 2 | LW  |     | 4 (R5)                                                                                                                                      |

| 3 | LW  |     | 0 (R2)                                                                                                                                      |

| 4 |     |     | R5, R3                                                                                                                                      |

| 5 | SW  |     | 0 (R5)                                                                                                                                      |

|   |     |     | oni NOP necessarie ad assicurare la corretta esecuzione del codice.                                                                         |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     | ema utilizzando istruzioni NOP solo quando i conflitti non possono essere inando le istruzioni.                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

|   |     |     |                                                                                                                                             |

| 3. Risolvere infine il problema supponendo che il processore sia dotato di propagazione e di             |

|----------------------------------------------------------------------------------------------------------|

| una unità di identificazione dei conflitti. Indicare inoltre il numero di cicli di clock totali e il CPI |

| N°         |   |   |   |   |   |   | Cicl | i di C | lock |    |    |    |    |    |    |

|------------|---|---|---|---|---|---|------|--------|------|----|----|----|----|----|----|

| Istruzioni | 1 | 2 | 3 | 4 | 5 | 6 | 7    | 8      | 9    | 10 | 11 | 12 | 13 | 14 | 15 |

|            |   |   |   |   |   |   |      |        |      |    |    |    |    |    |    |

|            |   |   |   |   |   |   |      |        |      |    |    |    |    |    |    |

|            |   |   |   |   |   |   |      |        |      |    |    |    |    |    |    |

|            |   |   |   |   |   |   |      |        |      |    |    |    |    |    |    |

|            |   |   |   |   |   |   |      |        |      |    |    |    |    |    |    |

|            |   |   |   |   |   |   |      |        |      |    |    |    |    |    |    |

|            |   |   |   |   |   |   |      |        |      |    |    |    |    |    |    |

|            |   |   |   |   |   |   |      |        |      |    |    |    |    |    |    |

| CICLI: |  |  |  |

|--------|--|--|--|

| CPI:   |  |  |  |

### **Domanda C**

Si consideri un sistema con uno spazio di indirizzamento di 16MByte ed due cache identiche (una cache dati ed una cache istruzioni) con le caratteristiche seguenti:

| Associatività     | Set associativa a 2 vie |  |  |  |

|-------------------|-------------------------|--|--|--|

| Dimensione totale | 32 KB                   |  |  |  |

| Dimensione linea  | 64 B (per ogni set)     |  |  |  |

| Tempo di accesso  | 1 ns                    |  |  |  |

Si indichi la struttura dell'indirizzo visto dalle cache, descrivendo i vari campi e il loro significato.

| Struttura dell'indirizzo |  |  |

|--------------------------|--|--|

|                          |  |  |

|                          |  |  |

|                          |  |  |

|                          |  |  |

|                          |  |  |

|                          |  |  |

|                          |  |  |

|                          |  |  |

|                          |  |  |

|                          |  |  |

|                          |  |  |

# Sapendo che:

- L'accesso alla memoria RAM avviene a parole di 32 bit

- Il tempo di accesso alla RAM in modalità normale è di 25 ns

- Il tempo di accesso alla RAM in modalità burst è

- o 50 ns per la prima parola

- o 10 ns per le parole successive

- L'hit rate della memoria dati è pari al 95%

- L'hit rate della memoria istruzioni e pari al 99.5%

Per ognuna delle due cache, si calcoli il tempo di accesso medio alla memoria

| Tempo medio di accesso D-Cache                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                              |

|                                                                                                                                                                              |

| Tempo medio di accesso I-Cache                                                                                                                                               |

|                                                                                                                                                                              |

|                                                                                                                                                                              |

|                                                                                                                                                                              |

|                                                                                                                                                                              |

| Infine, sapendo che in un dato programma il 60% delle istruzioni accedono alla memoria, si calcoli il tempo medio di esecuzione di una istruzione per il programma in esame. |

| Tempo di esecuzione:                                                                                                                                                         |

|                                                                                                                                                                              |

|                                                                                                                                                                              |

|                                                                                                                                                                              |

|                                                                                                                                                                              |

#### Domanda D

Si consideri il seguente insieme di processi:

| Processo | Tempo di Arrivo (TA) | Tempo di Esecuzione (TE) |

|----------|----------------------|--------------------------|

| P1       | 0                    | 6                        |

| P2       | 3                    | 2                        |

| P3       | 4                    | 3                        |

| P4       | 7                    | 5                        |

| P5       | 9                    | 1                        |

Si esegua lo scheduling di tali processi secondo i due seguenti algoritmi:

- 1. Round Robin, con un quanto di tempo pari a 3 unità

- 2. Shortest Remaining Time

Per ognuno dei due casi, quindi, si svolgano i seguenti punti:

- Si calcoli il tempo di attesa medio TW dei processi

- Si calcoli il rapporto di prestazioni R dei processi

#### Round Robin

| Processo | Tempo di Attesa (T <sub>W</sub> ) | Rapporto di Prestazioni (R) |

|----------|-----------------------------------|-----------------------------|

| P1       |                                   |                             |

| P2       |                                   |                             |

| Р3       |                                   |                             |

| P4       |                                   |                             |

| P5       |                                   |                             |

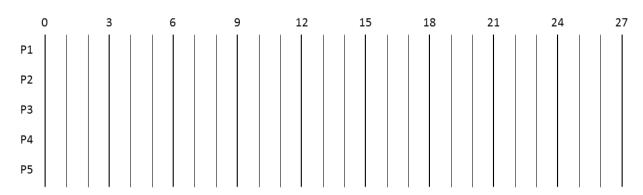

# **Shortest Remaining Time**

| 0  | 3 | 6 | 9 | 12 | 15 | 18 | 21 | 24 | 27 |

|----|---|---|---|----|----|----|----|----|----|

| P1 |   |   |   |    |    |    |    |    |    |

| P2 |   |   |   |    |    |    |    |    |    |

| Р3 |   |   |   |    |    |    |    |    |    |

| P4 |   |   |   |    |    |    |    |    |    |

| P5 |   |   |   |    |    |    |    |    |    |

| Processo | Tempo di Attesa (T <sub>w</sub> ) | Rapporto di Prestazioni (R) |

|----------|-----------------------------------|-----------------------------|

| P1       |                                   |                             |

| P2       |                                   |                             |

| Р3       |                                   |                             |

| P4       |                                   |                             |

| P5       |                                   |                             |

#### Domanda E

Un sistema dotato di memoria virtuale con paginazione e segmentazione di tipo UNIX è caratterizzato dai parametri seguenti:

- La memoria fisica ha capacità di 32 Kbyte

- La memoria logica ha capacità di 32 Kbyte

- La pagina di memoria ha dimensione di 4 Kbyte

| Si definisca la struttura degli indirizzi fisico e logico indicando la lunghezza dei | campi NPF, |

|--------------------------------------------------------------------------------------|------------|

| Spiazzamento fisico, NPL, Spiazzamento logico                                        |            |

Nel sistema vengono creati alcuni processi, indicati nel seguito con P, Q, R, S. I programmi eseguiti da tali processi sono due: X e Y. La dimensione iniziale dei segmenti dei programmi è la seguente:

CX: 8K DX: 4K PX: 4K CY: 12K DY: 8K PY: 4K

Si inserisca in tabella sottostante la struttura in pagine della memoria virtuale.

| NPV | Programma X | Programma Y |

|-----|-------------|-------------|

| 0   |             |             |

| 1   |             |             |

| 2   |             |             |

| 3   |             |             |

| 4   |             |             |

| 5   |             |             |

| 6   |             |             |

| 7   |             |             |

#### Sapendo che:

- L'esecuzione di un programma avviene caricando solamente la pagina di codice con l'istruzione di partenza e una sola pagina di pila

- Il caricamento di pagine ulteriori è in Demand Paging (cioè le pagine si caricano su richiesta senza scaricare le precedenti fino al raggiungimento del numero massimo di pagine residenti)

- L'indirizzo dell'istruzione di partenza di X è 0x14AF

- L'indirizzo dell'istruzione di partenza di Y è 0x0231

- Il numero di pagine residenti R vale 3;

- Viene utilizzato l'algoritmo LRU (ove richiesto prima si de-alloca una pagina di processo e poi si procede alla nuova assegnazione);

- Le pagine meno utilizzate in ogni processo sono quelle caricate da più tempo, con la sola eccezione seguente: se è residente una sola pagina di codice, quella è certamente stata utilizzata recentemente

A un certo istante di tempo sono terminati, nell'ordine, gli eventi seguenti:

- 1. Creazione del processo P e lancio del programma Y ("fork" di P ed "exec" di Y);

- 2. Creazione del processo Q e lancio del programma X ("fork" di Q ed "exec" di X);

- 3. Accesso ad un dato all'indirizzo 0x3ABC da parte di P;

- 4. Creazione di una nuova pagina di pila da parte di P;

- 5. Accesso ad un dato all'indirizzo 0x2158 da parte di Q;

- 6. Creazione del processo R come figlio di P ("fork" eseguita da P);

- 7. Creazione di 1 pagina di pila da parte di R.

Si riporti nella tabella seguente una descrizione dello stato della memoria fisica al termine della sequenza di operazioni di cui sopra. Al termine dell'operazione si riporti lo stato dell'MMU per quanto riguarda il processo P.

| Memoria Fisica |               |  |

|----------------|---------------|--|

| Ind.           | Pag. Allocate |  |

| Fisico         | -             |  |

| 0              |               |  |

| 1              |               |  |

| 2              |               |  |

| 3              |               |  |

| 4              |               |  |

| 5              |               |  |

| 6              |               |  |

| 7              |               |  |

| MMU |     |     |          |  |

|-----|-----|-----|----------|--|

| PID | NPV | NPF | Validità |  |

|     |     |     |          |  |

|     |     |     |          |  |

|     |     |     |          |  |

|     |     |     |          |  |

|     |     |     |          |  |

|     |     |     |          |  |

|     |     |     |          |  |

|     |     |     |          |  |

|     |     |     |          |  |

|     |     |     |          |  |

| Domanda F Si descrivano in modo chiaro i principali meccanismi di sincronizzazione tra thread. |  |  |  |

|------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |

|                                                                                                |  |  |  |